FPGA駆動用のPOL, LDOの評価試験

POL (Point of Load) やLDO (Low drop out) に代表されるDC/DCコンバータは、0.8V、1.2Vと非常に低い電圧出力となります。また、電源の供給先に使用されるFPGAはスイッチング素子 の集合体となり電流が急峻に変化します。このようなDC/DCコンバータの評価には、低電圧領域にて急峻な電流応答を再現可能な高速電子負荷が最適です。簡単にFPGAの擬似負荷として使用することができます。

| 従来の電子負荷装置の場合 | 高速低電圧電子負荷装置の場合 | |

| FPGA疑似動作 |  |  |

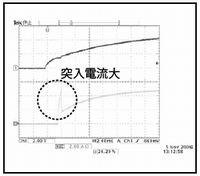

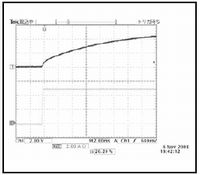

| 突入電流が発生し、設定電流に到達するまでに時間がかかります | 突入電流が無く、設定電流までに遅延無く急峻な立ち上がり特性です。 |

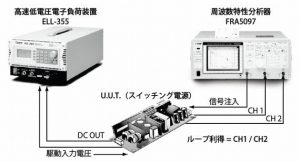

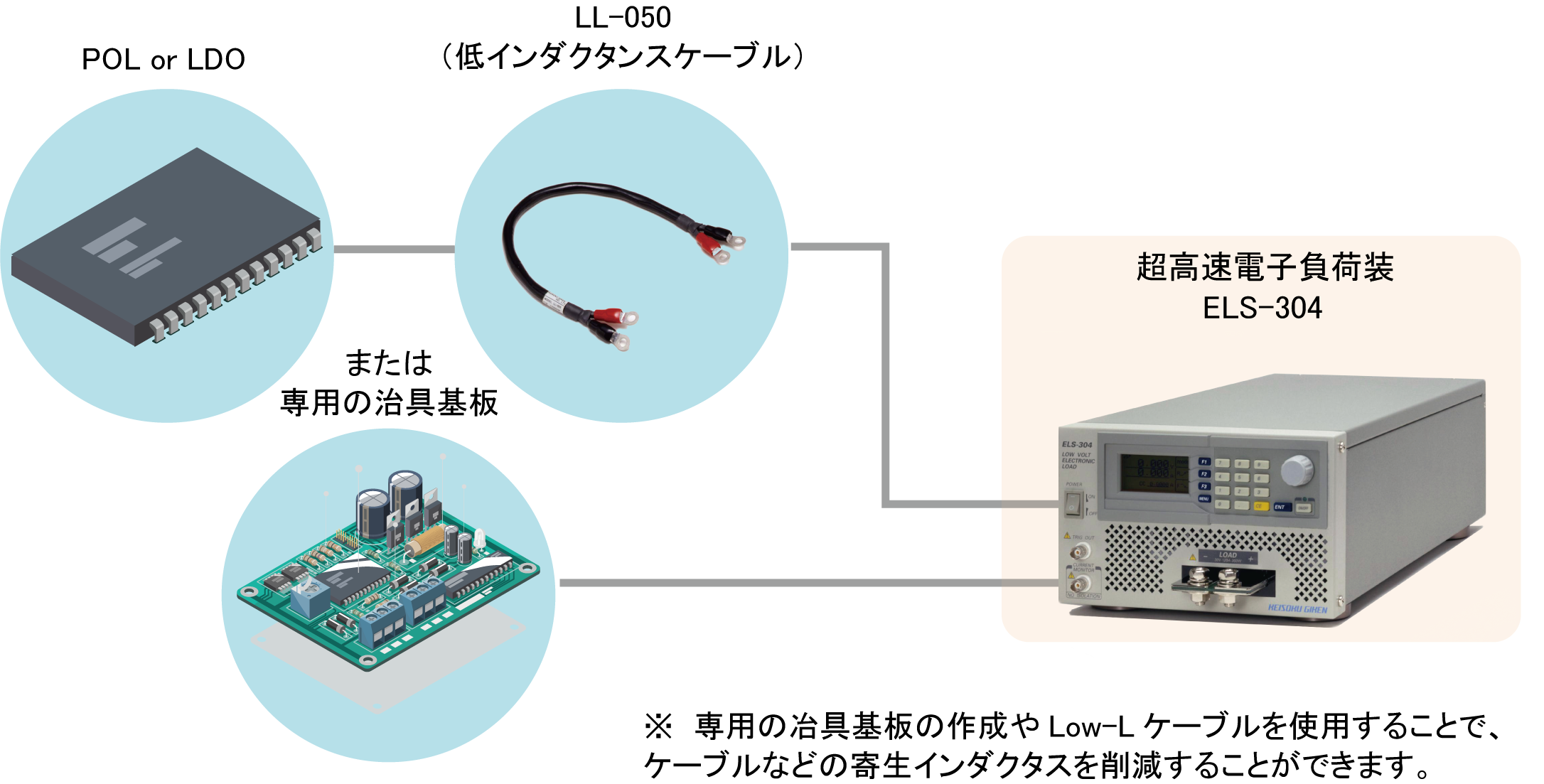

POL、LDO の電源評価の構成図

製品情報

| 製品名 | 型名 | 主な仕様 |

|---|---|---|

| 高速電子負荷装置 | ELS-304 |

本アプリケーションに記載された情報は作成発行当時(発行年月日)のものとなりますので、現行としてシリーズ・機種・型式(オプション含む)が変更(後継含め)及び販売終了品による廃型になっているものが含まれておりますので、予めご了承下さい。

本情報はテストソリューションにおけるDUT(供試体)・JIG及び当社製品のアプリケーション構成フローのご参考としてご覧下さい。

お気軽にお問い合わせください。044-223-79509:00-18:00 [土日・祝日除く]

お問い合わせ